Blackfin DSP Ausbildung

With the Blackfin DSP family, discover a solution both to your signal processing needs (double ALU 16 / 32 bits, up to 2400 MMAC) and to your connectivity needs (audio ADC and fast ADC, video, USB, Ethernet, etc.).

During this training, you will learn to make the best of this DSP to implement your signal processing functions.

Duration of training

Two daysDate and place of training

Place: Toulouse (France), date : contact us.

Contents

General architecture

- Architecture (registers, ALU, adressing, sequencer, pipeline),

- Memory architecture (L1, L2, L3 hierarchy, address map, explicite mapping of data / code),

- Cache memory (principle of associative cache, management of cache coherency),

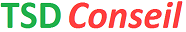

- Interruptions management (vectors, mapping from ISR sources to ISR vectors),

- DMA (1D and 2D),

- Execution modes,

- Booting of the processor (type of booting, format of the boot stream).

Signal processing

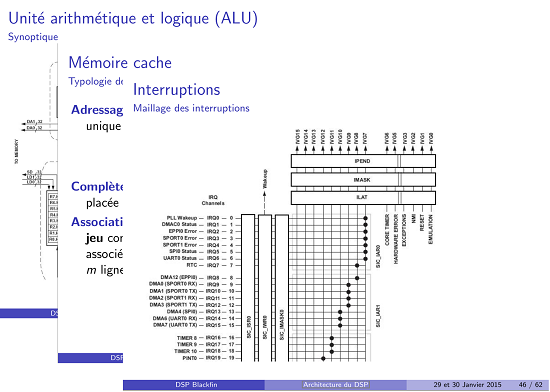

- Fixed point computing,

- Signal processing functions integrated into Visual DSP (filtering, FFT, etc.),

- Tutorial: Implementation of the Hilbert transform with the FFT (on evaluation board or simulator)

- Introduction to Blackfin assembler

- Tutorial: realization of an optimized dot product

Peripherals and power saving modes

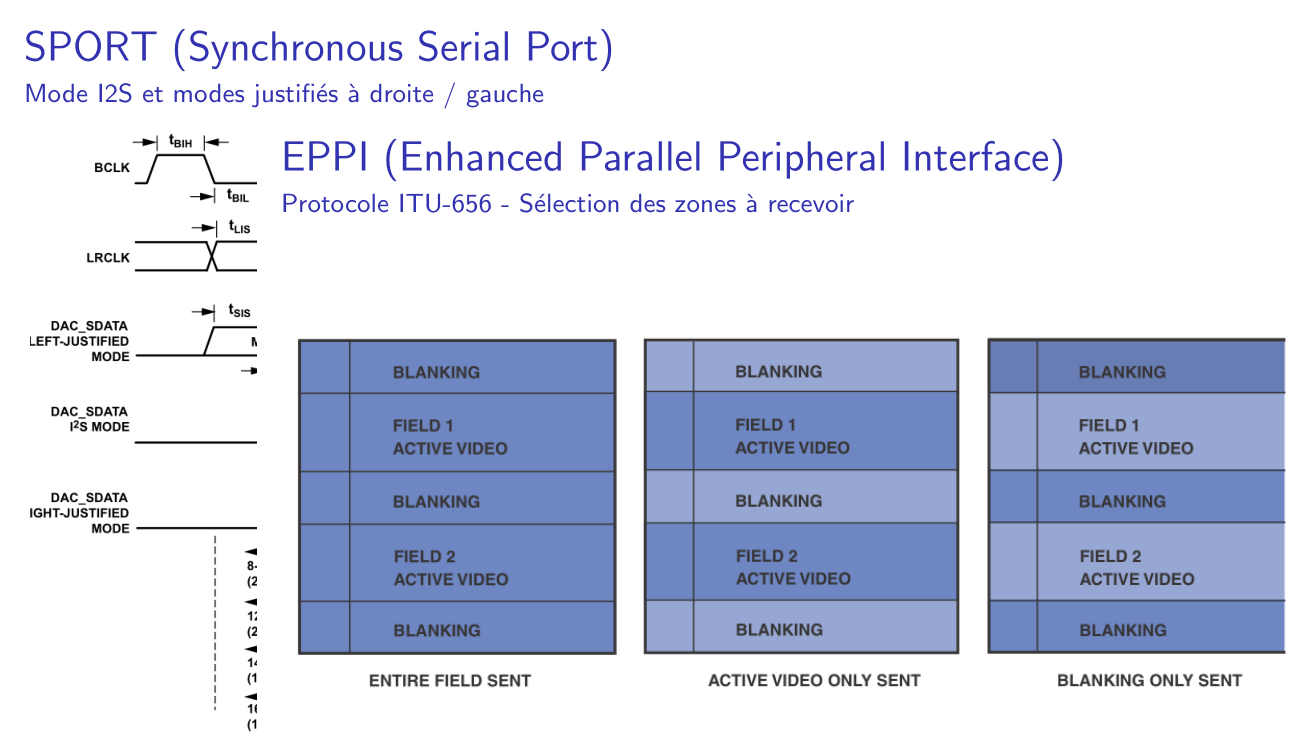

- Input / output peripherals,

- Communication protocols (CAN, Ethernet, USB),

- Memories (SDRAM / DDR / flash),

- Power management (tuning of the different clocks, core voltage, power saving modes)

Presentation of the new BF70x family

- Specifications (internal memories, new Blackfin+ core (MAC 32 bits / complex computing), consumption

- Special peripherals (ADC, host SPI port (SPIHP), generic counter (CNT)),

- Hardware accelerators for cryptography (hardware random generator, public key protocols, DES, AES, ARC4 accelerators, hashing tables (MD5, SHA, ...), PRBS sequences).